小科普:一分钟认识5代内存

随着CPU性能的不断提高,我们对内存性能的要求也逐步升级。同样,高性能的内存搭配高性能的CPU才能最大的发挥它的价值与优势。在为CPU选择匹配内存前,咱们可以简单了解一下内存的发展过程。

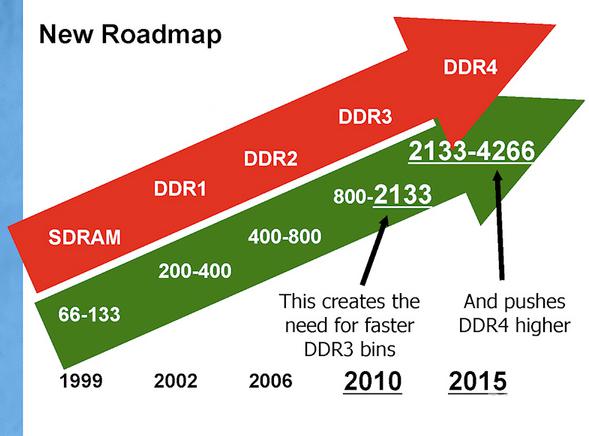

图1 SDRAM Roadmap

SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,咱们在此简称内存。SDRAM发展到现在已经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

图2 SDRAM

SDRAM内部组成可以分为几个部分,存储阵列、IO门控单元、行列地址解码器、行列地址锁存器、逻辑控制单元(包含模式寄存器)、数据输入输出寄存器等。

存储容量大小和数据位宽度、行地址、列地址、块数量等的关系:

DDR SDRAM(Dual Date Rate SDRAM)简称DDR,也就是“双倍速率SDRAM“。DDR在时钟信号上升沿与下降沿各传输一次数据,使得其数据传输速度为传统SDRAM的两倍。

DDR2 SDRAM相较于上一代整体布局变化不大,在输入输出数据总线接口上变化比较多。DDR2 能够在100MHz 的发信频率基础上提供每插脚最少400MB/s 的带宽,而且其接口将运行于1.8V 电压上,从而进一步降低发热量,以便提高频率。此外,DDR2也融入CAS、OCD、ODT 等新性能指标和中断指令,提升内存带宽的利用率。

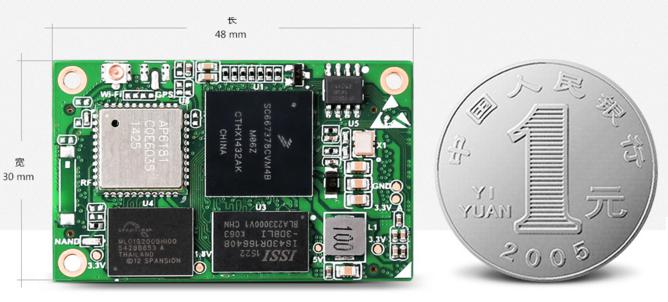

图4 基于DDR2的Wi-Fi工业级核心板

DDR3 SDRAM相比DDR2有更低的工作电压,从DDR2的1.8V降落到1.5V,性能更好、更为省电;同时将DDR2的4bit预读升级为8bit预读,目前最高能够支持1600Mhz的速度。

DDR3 在存储结构上改进工艺,允许堆叠更多的存储块,提高单颗芯片的容量;在功能上也增加了读写平衡。

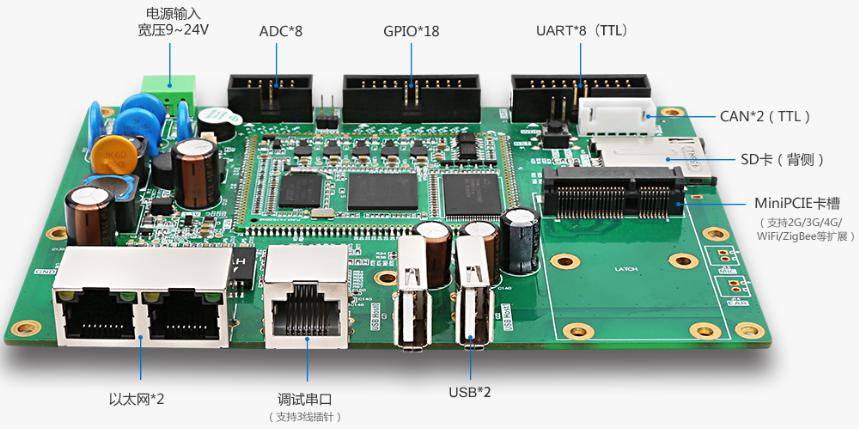

图5 基于DDR3的8串口双网口工控主板

DDR4 SDRAM在输入输出数据总线接口上继续改善性能,在存储结构上继续改进工艺,不仅堆叠更多的存储块,而且使用硅片穿孔工艺把把堆叠成的存储块进行并列放置,集中到一颗芯片中,提高单颗芯片的容量。

DDR4内存有两种规格。其中使用Single-endedSignaling信号的DDR4内存其传输速率已经被确认为 1.6~3.2Gbps,而基于差分信号技术的DDR4内存其传输速率则将可以达到6.4Gbps。